# 104-AIO16A and 104-AIO16E

# PC/104 HIGH-PERFORMANCE ANALOG I/O BOARDs

**USER MANUAL**

M104-AIO16A.A1j

#### **Notice**

The information in this document is provided for reference only. ACCES does not assume any liability arising out of the application or use of the information or products described herein. This document may contain or reference information and products protected by copyrights or patents and does not convey any license under the patent rights of ACCES, nor the rights of others.

IBM PC, PC/XT, and PC/AT are registered trademarks of the International Business Machines Corporation.

Printed in USA. Copyright 2008 by ACCES I/O Products, Inc. 10623 Roselle Street, San Diego, CA 92121. All rights reserved.

#### **WARNING!!**

ALWAYS CONNECT AND DISCONNECT YOUR FIELD CABLING WITH THE COMPUTER POWER OFF. ALWAYS TURN COMPUTER POWER OFF BEFORE INSTALLING A BOARD. CONNECTING AND DISCONNECTING CABLES, OR INSTALLING BOARDS INTO A SYSTEM WITH THE COMPUTER OR FIELD POWER ON MAY CAUSE DAMAGE TO THE I/O BOARD AND WILL VOID ALL WARRANTIES, IMPLIED OR EXPRESSED.

#### Warranty

Prior to shipment, ACCES equipment is thoroughly inspected and tested to applicable specifications. However, should equipment failure occur, ACCES assures its customers that prompt service and support will be available. All equipment originally manufactured by ACCES which is found to be defective will be repaired or replaced subject to the following considerations.

#### **Terms and Conditions**

If a unit is suspected of failure, contact ACCES' Customer Service department. Be prepared to give the unit model number, serial number, and a description of the failure symptom(s). We may suggest some simple tests to confirm the failure. We will assign a Return Material Authorization (RMA) number which must appear on the outer label of the return package. All units/components should be properly packed for handling and returned with freight prepaid to the ACCES designated Service Center, and will be returned to the customer's/user's site freight prepaid and invoiced.

#### Coverage

First Three Years: Returned unit/part will be repaired and/or replaced at ACCES option with no charge for labor or parts not excluded by warranty. Warranty commences with equipment shipment.

Following Years: Throughout your equipment's lifetime, ACCES stands ready to provide on-site or in-plant service at reasonable rates similar to those of other manufacturers in the industry.

#### **Equipment Not Manufactured by ACCES**

Equipment provided but not manufactured by ACCES is warranted and will be repaired according to the terms and conditions of the respective equipment manufacturer's warranty.

#### General

Under this Warranty, liability of ACCES is limited to replacing, repairing or issuing credit (at ACCES discretion) for any products which are proved to be defective during the warranty period. In no case is ACCES liable for consequential or special damage arriving from use or misuse of our product. The customer is responsible for all charges caused by modifications or additions to ACCES equipment not approved in writing by ACCES or, if in ACCES opinion the equipment has been subjected to abnormal use. "Abnormal use" for purposes of this warranty is defined as any use to which the equipment is exposed other than that use specified or intended as evidenced by purchase or sales representation. Other than the above, no other warranty, expressed or implied, shall apply to any and all such equipment furnished or sold by ACCES.

#### **Ordering Guide**

- 104-AIO16A Full featured version with 16-Bit 500kHz A/D

- 104-AIO16E Economy version with 16-Bit 250kHz A/D

#### Optional accessories

- 104-STA-16A In-stack Screw Terminal Board with interconnecting ribbon cables (2)

- 104-SPC-KIT Spacer kit (16-bit PC/104 pass-through connector and hardware kit)

- 104-HDW-KIT(X) Mounting hardware kit (X=M (Metric) or S (Standard))

- 104-BP2 Dual PC/104 backplane

- Ribbon cables and a variety of terminal connection accessories are also available

## **TABLE OF CONTENTS**

| Ordering Guide                                                          | 3  |

|-------------------------------------------------------------------------|----|

| Optional accessories                                                    |    |

| Chapter 1: Introduction                                                 | 5  |

| Features                                                                |    |

| Functional Description                                                  |    |

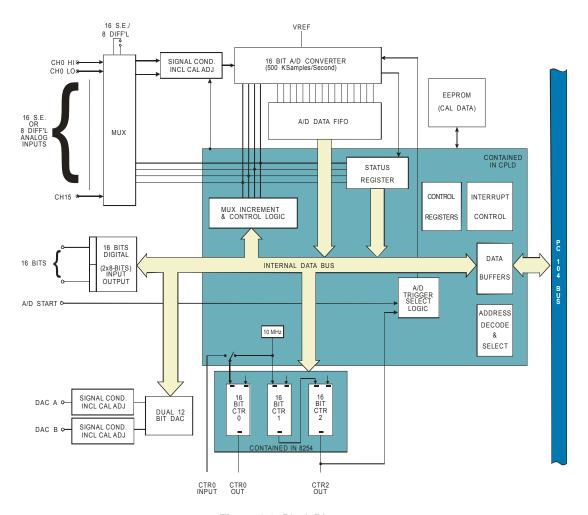

| Figure 1-1: Block Diagram                                               |    |

| Analog Inputs                                                           | 6  |

| Table 1-1: Analog Input Range Selection                                 |    |

| A/D Start                                                               | 7  |

| Oversample                                                              | 7  |

| Calibration                                                             | 7  |

| A/D FIFO                                                                | 8  |

| Interrupt Request (IRQ)                                                 | 8  |

| Analog Outputs (DAC)                                                    |    |

| Digital I/O                                                             |    |

| Counter/Timer                                                           |    |

| Model Options                                                           |    |

| Included with your board                                                |    |

| Chapter 2: Installation                                                 |    |

| Software CD Installation                                                |    |

| To Install the Board                                                    |    |

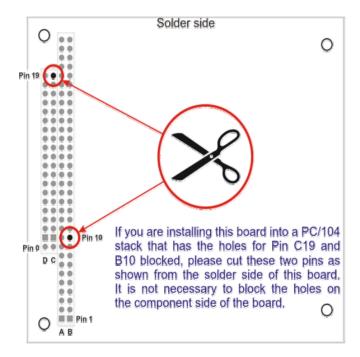

| Figure 2-1: PC/104 Key Information                                      |    |

| Chapter 3: Option Selection                                             |    |

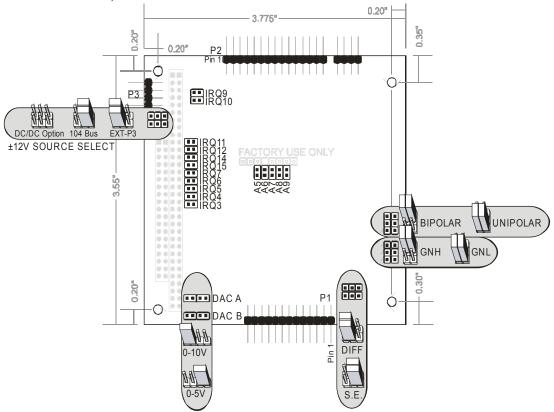

| Figure 3-1: Option Selection Map                                        | 12 |

| Setting the Base Address                                                | 13 |

| Table 3-1: Base Address Jumper Configuration                            | 13 |

| Chapter 4: Base Address Selection                                       | 14 |

| Table 4-1: Hex Conversion                                               | 14 |

| Chapter 5: Programming                                                  | 15 |

| Table 5-1: Register Definitions                                         |    |

| Writing to the EEPROM                                                   |    |

| Reading from the EEPROM                                                 |    |

| Chapter 6: Connector Pin Assignments                                    |    |

| Table 6-1: P1, 26-pin Right-Angle Header, Analog Inputs, Analog Outputs |    |

| Table 6-2: P2, 44-pin Right-Angle Header, Digital I/O & Counter/Timers  | 26 |

| Table 6-3: P3, 8-pin Right-Angle Header, External Power                 |    |

| Chapter 7: Specifications                                               |    |

| Analog Inputs                                                           |    |

| Digital I/O                                                             |    |

| Environmental                                                           |    |

| Appendix A: 82C54 Counter Timer Operation                               | 28 |

| Operational Modes                                                       |    |

| Programming                                                             |    |

| Reading and Loading the Counters                                        |    |

| Appendix B: Calibration                                                 |    |

| Breakdown: Calibrating the DACs                                         |    |

| Step-By-Step: Calibrating the DACs                                      |    |

| Breakdown: Calibrating the A/D                                          |    |

| Step-By-Step: Calibrating the A/D                                       |    |

| Table B-1: Factory EEPROM Calibration Locations                         |    |

| Customer Comments                                                       | oo |

## **Chapter 1: Introduction**

This PC/104 based Data Acquisition Module is an ideal solution for embedded applications requiring high-resolution and high-speed analog input, analog output, and digital I/O capabilities. This manual applies to both the "16A" version and the "16E" version, with the primary difference being the achievable sampling speed. Wherever a reference is made to a sampling frequency or clock frequency, 500k applies only to the "16A" version, while 250k applies only to the "16E" version.

#### **Features**

- 16-bit resolution A/D

- Sampling rate

- "16A" version: 500Ksamples/sec (maximum aggregate) "16E" version: 250Ksamples/sec (maximum aggregate)

- 16 single-ended or 8 differential analog inputs

- Channel-by-channel ranges of 0-1V, 0-2V, 0-5V, 0-10V, ±1V, ±2V, ±5V, ±10V

- A/D Start sources: Software, Timer, and External Trigger (rising or falling edge; software selectable)

- A/D Modes: Single Channel or Scan

- Offset / Gain Error Calibration

- Noise reduction with Channel Oversampling

- Over-voltage protection of -40V to +55V

- First In First Out (FIFO) A/D buffer

- Two 12-bit Digital-to-Analog (DAC) outputs

- DAC error calibration

- 16 high-current Digital I/O lines

- 16-bit programmable counter/timer

- PC/104 module size and mounting compatibility

#### **Applications**

- Equipment monitoring

- Environmental measurements

- Embedded data acquisition

- Education/Laboratory

#### **Functional Description**

This product is a PC/104-based Analog to Digital converter board with 16 single-ended or 8 differential analog inputs. The board is capable of sampling speeds up to 500k. Analog input channels are enabled as a consecutive set by software. Each channel within the set is independently configured by jumpers+software to accept one of ten different analog input ranges.

Analog to digital conversion starts or "A/D starts" are issued one of three ways: Software Start, Timer Start, or External Trigger Start. A/D starts are software configured to be either rising or falling edge. Additionally, A/D starts are software configured to be Single Channel or Scan. Single Channel samples data once from the next consecutive channel within the enabled set. A Scan samples data from all channels within the set at the fastest possible rate. An onboard FIFO allows the analog data to be buffered and read out at a later time. The FIFO has two flags, FIFO half-full and FIFO full, which can both trigger an IRQ.

Two 12-bit DAC outputs are provided. Output ranges of 0-5V and 0-10V are field selectable with jumpers, per output.

Also provided are 16 Digital I/O lines in 2 groups of 8 lines. Both Digital I/O bytes are individually software selectable as input or output.

Manual 104-AIO16A and 104-AIO16E

Page 5/40

A fully programmable 8254 16-bit counter is provided with a maximum input frequency of 10MHz. The clock and output can be accessed externally for extended functionality.

Figure 1-1: Block Diagram

#### **Analog Inputs**

There are a total of 16 single-ended or 8 differential analog inputs on this board. A consecutive set of channels are enabled/disabled by software. This set of channels is constructed by a start and end channel. Sampling begins on the start channel and continues through every successive channel until the end channel is sampled. Once the end channel has been sampled, the process repeats again from the start channel. All channels within the set are jumper configured as either single-ended or differential.

10 input ranges, 6 bipolar and 4 unipolar, are selectable by jumpers+software. Each jumper configuration allows four voltage ranges to be configured by software for each individual channel (Table 1-1). The unipolar ranges are 0-1V, 0-2V, 0-5V, and 0-10V. The bipolar ranges are  $\pm 0.5V$ ,  $\pm 1$ ,  $\pm 2V$ ,  $\pm 2.5V$ ,  $\pm 5V$ , and  $\pm 10V$ . Refer to the option selection map for jumper range settings.

Each channel input has an over-voltage protection of -40V to +55V.

|                                                               | Table 1-1: Analog Input Range Selection |         |        |        |        |  |  |  |  |  |  |

|---------------------------------------------------------------|-----------------------------------------|---------|--------|--------|--------|--|--|--|--|--|--|

| Jumpers SoftwareGain=0 SoftwareGain=1 SoftwareGain=2 Software |                                         |         |        |        |        |  |  |  |  |  |  |

| GNH                                                           | Unipolar                                | 0 - 10V | 0 - 5V | 0 - 2V | 0 - 1V |  |  |  |  |  |  |

|                                                               | Bipolar                                 | ± 5V    | ± 2.5V | ± 1V   | ± 0.5  |  |  |  |  |  |  |

| GNL                                                           | Bipolar                                 | ± 10V   | ± 5V   | ± 2V   | ± 1V   |  |  |  |  |  |  |

#### A/D Start

This board offers three software selectable sources for A/D Start: Software Start, Timer Start, and External Start Trigger. Software Start generates an A/D Start every time the software command is issued. Timer Start uses the on-board timer to generate an A/D Start. Frequencies ranging from 2.33 \*  $10^{3}$ Hz to 500kHz are possible with Timer Start. External Start Trigger uses the External Trigger pin on the connector to generate an A/D Start. Frequencies up to 500kHz are allowed for External Start Trigger.

A/D Start is also software configured as rising or falling edge.

An A/D Start can be one of two software selectable types for this board: Single Channel or Scan. A/D Starts that are Single Channel sample one channel within the enabled set per A/D Start. This allows for total control over the time skew between channels.

Scan, on the other hand, will sample all the channels within the enabled set per A/D Start. Channels are sampled at 500kHz to minimize the time skew between channels.

#### **Oversample**

To minimize noise, the board implements a technique called Oversampling. Oversampling is a technique which continuously samples a channel multiple times at 500kHz. Quickly taking several samples from the same channel allows the signal to be averaged. Averaging a signal can greatly reduce the noise injected by both the signal and the board/system.

The oversample range is from 0 to 255 (software selectable) and applies to every channel within the enabled set. A channel is always sampled once plus the number of oversamples that was configured. Therefore an oversample of 0 will sample a channel once (initial sample plus 0 oversamples), oversample of 1 will sample a channel twice (initial sample plus 1 oversample), up to an oversample of 255 which will sample a channel 256 times (initial sample plus 255 oversamples).

Each channel's oversamples are taken before sampling begins on the next consecutive channel within the enabled set.

#### Calibration

All Analog-to-Digital Converters (ADCs) suffer from offset and gain errors. To account for this, the board implements calibration hardware to adjust for the offset/gain errors. This is particularly helpful as aging occurs and/or operating temperature changes.

The gain and offset are individually adjusted by means of digital potentiometers. Constants are loaded into the potentiometers which are used to make these adjustments. If constants are not loaded, the potentiometers will be set to the center of their ranges by default. Therefore, for maximum accuracy, appropriate constants should be loaded each time the board is powered. Refer to Chapter 5: Programming and Appendix B: Calibration for information on how to determine and load appropriate constants.

#### A/D FIFO

The A/D FIFO buffers the data out of the ADC. This allows conversions to happen without constant CPU intervention. Furthermore, the FIFO's half-full and full flags are readable by software. They can also be used to generate interrupts. If the FIFO becomes full, A/D conversions are paused and resume when at least one A/D sample is read out of the FIFO.

#### **Interrupt Request (IRQ)**

This board can be software enabled to generate an IRQ when the A/D FIFO becomes half-full or full. An IRQ can also be generated after the end of a conversion (EOC) or after the end of a scan (EOS). These IRQs help in taking A/D data off the board quickly.

The selection of the IRQ to be used is made by selecting one of the IRQ jumpers on the board. The location of these jumpers is shown in the Option Selection Map.

Place a jumper on the posts corresponding to the IRQ you wish to select. If you do not intend on using IRQs, do not install a jumper on any IRQ pins.

#### **Analog Outputs (DAC)**

There are two analog outputs on this board. Each analog output is adjusted by output calibration circuitry including a digital potentiometer. The DACs have two output ranges of 0-5V or 0-10V. These are individually chosen through jumper selections on the board. Refer to the option selection map for the jumper selections. Please note that the DACs are labeled DAC A and DAC B on the PC board but typically referred to as DAC 0 and DAC 1 in the manual. These terms are interchangeable as DAC 0 is the same as DAC A, DAC 1 the same as DAC B.

The digital calibration potentiometers are serial devices, with data being entered bit by bit. Although the details of writing bit by bit are described in Appendix B, it is expected that data will be loaded using a software subroutine. Make sure that the correct calibration constants are loaded into the digital potentiometers before using the analog outputs. Refer to Appendix B for calibrating the DACs.

Lastly, the DACs have a mode of operation called simultaneous update that will update both DACs simultaneously after DAC1 has been written to. Otherwise, each DAC will update upon being written to. Refer to Chapter 5: Programming for configuration details.

#### Digital I/O

This board contains an 8255 like Programmable Peripheral Interface (PPI). There are 2 ports, A and B, available for Digital I/O. Both the low byte (port A) and high byte (port B) can be individually software configured as inputs or outputs. In output mode, each port supports readback of the last written values. Each DIO line is capable of sourcing 24mA or sinking 24mA. By default the DIO lines are pulled up with a  $10 \mathrm{K}\Omega$  resistor to 5V.

#### Counter/Timer

The highly versatile 8254 contains three counter/timers. Counter/Timer 0 is available for general purpose use. Counter/Timer 1&2 are dedicated for use in timing A/D starts. The output of Counter/Timer 2 is available on the P2 connector.

Counter/Timer 0's clock and output signals are brought out to the connector. Both signals are buffered and capable of sourcing 24mA or sinking 24mA. Counter/Timer 0's clock is pulled up with a  $10K\Omega$  resistor to 5V.

Counter/Timer 0's clock input is software selectable between an internal 10MHz clock and the external Counter/Timer 0 clock on the P2 connector. The maximum allowed frequency for the clock is 10MHz.

## **Model Options**

- -DC Onboard DC/DC converter enables operation from a single +5V power supply

- -T Extended Temperature Operation (-40° to +85°C)

- -FIFOx "x" = FIFO sample capacity

- o 2K, 4K (1K is standard size)

- -S0x Special number designator, application specific, contact factory

- o Examples: latching I/O connectors; configuration jumpers factory set

## Included with your board

The following items are included with your shipment. Please take time now to ensure that no items are damaged or missing.

- 1. PC/104 Analog and Digital I/O Module

- 2. Software Master CD (PDF user manual installed with product package)

- 3. Printed I/O Quick-Start Guide

## **Chapter 2: Installation**

You may wish to refer to the printed I/O Quick Start Guide which was included with your product shipment for specific, quick steps to complete the hardware and software installation.

#### Software CD Installation

The software provided with this board is contained on one CD and *must be installed onto your hard disk prior to use.* To do this, perform the following steps as appropriate for your operating system. Substitute the appropriate drive letter for your drive where you see D: in the examples below.

#### WIN98/Me/2000/XP/2003

- a. Place the CD into your CD-ROM drive.

- b. The CD should automatically run the install program. If the install program does not run, click START | RUN and type DIINSTALL, click OK or press

- c. Follow the on-screen prompts to install the software for this board.

#### LINUX

a. Please refer to linux.htm on the CD-ROM for information on installing under linux.

#### **Hardware Installation**

Install the software package and set all hardware configuration jumpers (refer to Chapter 3, Option Selection) before plugging the hardware into the system. The SETUP Program can also be used to assist in configuring jumpers on the board. Be especially careful with Address Selection. If the addresses of two installed functions overlap, you will experience unpredictable computer behavior. To help avoid this problem, refer to the FINDBASE.EXE program installed from the CD. The setup program does not set the options on the board, these must be set by jumpers.

Caution! \* ESD A single static discharge can damage your card and cause premature failure! Please follow all reasonable precautions to prevent a static discharge such as grounding yourself by touching any grounded surface prior to touching the card.

#### To Install the Board

- Install jumpers for selected options and base address according to your application requirements, as mentioned above.

- 2. Remove power from the PC/104 stack.

- 3. Assemble standoff hardware for stacking and securing the boards.

- 4. Carefully plug the board onto the PC/104 connector on the CPU or onto the stack, ensuring proper alignment of the pins before completely seating the connectors together.

- 5. Install I/O cables onto the board's I/O connectors and proceed to secure the stack together or repeat steps 3-5 until all boards are installed using the selected mounting hardware.

- Check that all connections in your system are correct and secure then power up the system.

- 7. Run one of the provided sample programs appropriate for your operating system that was installed from the CD to test and validate your installation.

Figure 2-1: PC/104 Key Information

## **Chapter 3: Option Selection**

Jumpers are available on the board to configure the following:

Base address, IRQ and +/-12V source selection

DAC output voltage ranges

A/D input mode (single ended or differential), range and bipolar / unipolar selections

Software can determine the jumper selections by reading the status register at Base Address +12 (see Chapter 5: Programming for more information).

Please refer to the Setup Program on the Software Master CD for additional details of selecting the appropriate options for your application. The standard board has a Counter/Timer, two 12-bit DAC Channels, 16 Bits of Digital I/O, and a 16 channel 16-bit A/D Converter with a 1k sample FIFO. There is an optional version of the board that provides an onboard DC/DC converter. If your PC/104 stack has +5V and +/-12V available, a DC/DC converter is not needed.

Figure 3-1: Option Selection Map

The board can take  $\pm 12V$  power from the PC/104 bus, an external source, or an optional DC/DC converter. If the DC/DC converter is installed on the board, the two jumpers next to P3 should not be installed, and their posts may be missing. If no DC/DC converter is present, the jumpers should be installed in their right positions to take  $\pm 12V$  power from the PC/104 bus, or the left positions (toward the edge of the board) to take  $\pm 12V$  power from an external source, provided via P3.

## **Setting the Base Address**

The following table provides a convenient reference for all address jumper configurations. "YES" indicates the jumper is installed.

| A9  | A8  | A7  | A6  | A5  | Address Range |

|-----|-----|-----|-----|-----|---------------|

| YES |     | YES | YES | YES | 100h - 11Bh   |

| YES |     | YES | YES |     | 120h - 13Bh   |

| YES |     | YES |     | YES | 140h - 15Bh   |

| YES |     | YES |     |     | 160h - 17Bh   |

| YES |     |     | YES | YES | 180h - 19Bh   |

| YES |     |     | YES |     | 1A0h - 1BBh   |

| YES |     |     |     | YES | 1C0h - 1DBh   |

| YES |     |     |     |     | 1E0h - 1FBh   |

|     | YES | YES | YES | YES | 200h - 21Bh   |

|     | YES | YES | YES |     | 220h - 23Bh   |

|     | YES | YES |     | YES | 240h - 25Bh   |

|     | YES | YES |     |     | 260h - 27Bh   |

|     | YES |     | YES | YES | 280h - 29Bh   |

|     | YES |     | YES |     | 2A0h - 2BBh   |

|     | YES |     |     | YES | 2C0h - 2DBh   |

|     | YES |     |     |     | 2E0h - 2FBh   |

|     |     | YES | YES | YES | 300h - 31Bh   |

|     |     | YES | YES |     | 320h - 33Bh   |

|     |     | YES |     | YES | 340h - 35Bh   |

|     |     | YES |     |     | 360h - 37Bh   |

|     |     |     | YES | YES | 380h - 39Bh   |

|     |     |     | YES |     | 3A0h - 3BBh   |

|     |     |     |     | YES | 3C0h - 3DBh   |

|     |     |     |     |     | 3E0h - 3FBh   |

Table 3-1: Base Address Jumper Configuration

## **Chapter 4: Base Address Selection**

The Board's Base Address is set by jumpers labeled "BOARD ADDR." The jumpers are marked /A5 through /A9, and /A5 is the least significant bit of the address. The base address can be selected anywhere within the I/O address range 000-3E0 provided that they do not overlap with other functions. The FINDBASE software utility provided on the CD with your board will help you select a base address that does not conflict with other assignments.

This board requires a block of 27 addresses (1B hex). Address Setup Jumper locations are marked /A5 through /A9. In order to configure the desired address, the hexadecimal address must be converted to a binary representation, which is then selected by installing jumpers on the board.

For example, as illustrated below, switch selection corresponds to hex **2C0** (or binary 10 110x xxxx). The "xxxxx" represents address lines A4 through A0 used on the board to select individual registers as described in Chapter 5: Programming.

| Hex Representation    | 2  |     | С  |    |     |

|-----------------------|----|-----|----|----|-----|

| Conversion Factors    | 2  | 1   | 8  | 4  | 2   |

| Binary Representation | 1  | 0   | 1  | 1  | 0   |

| Jumper Installed      | NO | YES | NO | NO | YES |

| Jumper Label          | A9 | A8  | A7 | A6 | A5  |

Table 4-1: Hex Conversion

Please note that "1" means that no jumper is installed and that "0" means that a jumper must be installed.

Consult the documentation for your system before selecting the board address. If you have doubts concerning available addresses in your particular computer, use the FINDBASE utility provided to determine available addresses.

Some embedded CPU boards mask out legacy I/O space and IRQ availability in CMOS. If you are having difficulty accessing this hardware using one of the installed sample programs, enter the CMOS to verify peripheral and I/O settings.

## **Chapter 5: Programming**

**A/D Order of Operations:** Behavior may become unpredictable if these steps are not followed. This is a guide of steps to take before beginning an A/D conversion.

- 1) Configure the channel gains (Base Address + 2-5).

- 2) Configure the start and end channel (Base Address + 6).

- 3) Configure the number of oversamples per channel (Base Address + 7).

- 4) Configure Counter/Timer 1&2 if using Timer Start or External Start Trigger (Base Address + 8-B). If using External Start Trigger, connect the trigger source to P2 pin 39.

- 5) Configure the A/D Start Source as Software Start, Timer Start, or External Start Trigger. Configure A/D Start as rising or falling edge. Configure A/D Start as Single Channel or Scan. (Base Address + 11). Once this address is written to, A/D conversions will be enabled if the A/D Start Source is either Timer Start or External Start Trigger. If the A/D Start Source is Software Start, conversions will begin after a write to Base Address + 1.

- 6) Read A/D data from the A/D Data FIFO with a read from Base Address + 0-1. It is helpful to use the flags in Base Address + 12 and the IRQ flags in Base Address + 13 when deciding to read A/D data.

| Offset | Write Function                 | Read Function                 |

|--------|--------------------------------|-------------------------------|

| 0      |                                | A/D Data                      |

| 1      | A/D Software Start             | AVD Data                      |

| 2      |                                |                               |

| 3      | A/D Programmable Gain          |                               |

| 4      | Configuration                  |                               |

| 5      |                                |                               |

| 6      | A/D Start/End Ch Configuration |                               |

| 7      | A/D Oversample Configuration   |                               |

| 8      |                                |                               |

| 9      | Counter/Timer Configuration    | Counter/Timer Configuration   |

| Α      | Counter/Timer Corniguration    | Oddriten Filmer Gornigaration |

| В      |                                |                               |

| С      | DAC 0 Output Data              |                               |

| D      | DAO 0 Output Data              |                               |

| E      | DAC 1 Output Data              |                               |

| F      |                                |                               |

| 10     | DAC Configuration              |                               |

| 11     | A/D Start & Counter/Timer 0    |                               |

|        | Clock Configuration            |                               |

| 12     |                                | A/D, DAC, FIFO Status Flags   |

| 13     | IRQ Configuration              | IRQ Status                    |

| 14     | Port A DIO (8255)              | Port A DIO (8255)             |

| 15     | Port B DIO (8255)              | Port B DIO (8255)             |

| 16     |                                |                               |

| 17     | DIO Configuration (8255)       |                               |

| 18     | EEPROM access                  | EEPROM access                 |

| 19     | Calibration access             |                               |

| 1A     |                                |                               |

| 1B     | Reset Register                 |                               |

| 1C-1E  |                                |                               |

| 1F     |                                | Board Model                   |

Table 5-1: Register Definitions

**NOTE:** Reading and writing words (16 bits) may only be done on even address boundaries (ie: Base Address + 0, + 2, etc). Reading and writing bytes (8 bits) can be done on even or odd boundaries.

| Base Addre |        | (read) | A/D Data |       |       |       |       |

|------------|--------|--------|----------|-------|-------|-------|-------|

| Bit 7      | Bit 6  | Bit 5  | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| ad7        | ad6    | ad5    | ad4      | ad3   | ad2   | ad1   | ad0   |

|            |        |        |          |       |       |       |       |

| Base Addre | ess +1 |        |          |       |       |       |       |

| Bit 7      | Bit 6  | Bit 5  | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| ad15       | 2d1/   | 2413   | 2412     | 2411  | 2410  | 240   | 248   |

#### ad15-ad0 -> A/D data

Reading a word from Base Address + 0 or two consecutive byte reads, first Base Address + 0 and then Base Address + 1, will grab one conversion's data from the A/D FIFO. If issuing two byte reads, it is important to know that the A/D FIFO increments to the next conversion's data only after the byte read from Base Address + 1. The byte read from Base Address + 0 must be done before the byte read from Base Address + 1 or the lower data byte will be lost.

| Base Address + 1 |                | (write) | A/D Softwa                    | re Start |  |  |  |  |  |

|------------------|----------------|---------|-------------------------------|----------|--|--|--|--|--|

| Bit 7            | Bit 6          | Bit 5   | Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |          |  |  |  |  |  |

|                  | Software start |         |                               |          |  |  |  |  |  |

Writing any value to this address will begin one A/D Start.

| Base Address + 2-5 | (write) | A/D Programmable Gain Configuration |

|--------------------|---------|-------------------------------------|

| Base Address +2    |         |                                     |

| Dasc Addic | .33 · Z  |          |          |          |          |          |          |

|------------|----------|----------|----------|----------|----------|----------|----------|

| Bit 7      | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

| Ch3 Soft   | wareGain | Ch2 Soft | wareGain | Ch1 Soft | wareGain | Ch0 Soft | wareGain |

# Base Address +3 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Ch7 SoftwareGain Ch6 SoftwareGain Ch5 SoftwareGain Ch4 SoftwareGain

| Base Addre | ess +4                        |       |          |          |          |          |          |

|------------|-------------------------------|-------|----------|----------|----------|----------|----------|

| Bit 7      | Bit 6                         | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

| Ch11 Sof   | Ch11 SoftwareGain Ch10 Softwa |       | wareGain | Ch9 Soft | wareGain | Ch8 Soft | wareGain |

| Base Addre | ess +5                                                                  |       |       |       |       |       |       |  |

|------------|-------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| Bit 7      | Bit 6                                                                   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

| Ch15 Sof   | Ch15 SoftwareGain Ch14 SoftwareGain Ch13 SoftwareGain Ch12 SoftwareGain |       |       |       |       |       |       |  |

softwareGain = "00" = 0 softwareGain = "01" = 1 softwareGain = "10" = 2 softwareGain = "11" = 3

Writing to these addresses will set the Software Gain per channel (see Table 1-1: Analog Input Range Selection)

| Base Addr | ess + 6 ( | (write) | A/D Start/E | nd Channel C | onfiguration |        |        |

|-----------|-----------|---------|-------------|--------------|--------------|--------|--------|

| Bit 7     | Bit 6     | Bit 5   | Bit 4       | Bit 3        | Bit 2        | Bit 1  | Bit 0  |

| end3      | end2      | end1    | end0        | start3       | start2       | start1 | start0 |

start3-start0 -> A/D start channel (0-15) end3-end0 -> A/D end channel (0-15)

Writing to this address will set the start and end address of the enabled set of channels.

| Base Address + 7 |           | write)    | e) A/D Oversample Configuration |           |           |           |           |  |

|------------------|-----------|-----------|---------------------------------|-----------|-----------|-----------|-----------|--|

| Bit 7            | Bit 6     | Bit 5     | Bit 4                           | Bit 3     | Bit 2     | Bit 1     | Bit 0     |  |

| overSamp7        | overSamp6 | overSamp5 | overSamp4                       | overSamp3 | overSamp2 | overSamp1 | overSamp0 |  |

overSamp7-overSamp0 -> Channel Oversample (0-254)

Writing to this address will set the number of oversamples to take per channel.

#### Base Address + 8-B Counter/Timer Configuration

Counter/Timer 0 is fully programmable for general use. Counter/Timer 1&2 are concatenated together (output of Counter/Timer 1 is routed to the clock input of Counter/Timer 2). The concatenated Counter/Timer 1&2 are used for A/D Start: both Timer Start and External Start Trigger. The output of Counter/Timer 2 is the source for the aforementioned A/D Starts. The output of Counter/Timer 2 is available on Pin 43 of connector P2.

For detailed information on programming the 8254 Counter/Timer device, please refer to Appendix A.

| Base Addre<br>Base Addre | ,      | (write) | DAC 0 Outp | out Data |       |       |       |

|--------------------------|--------|---------|------------|----------|-------|-------|-------|

| Bit 7                    | Bit 6  | Bit 5   | Bit 4      | Bit 3    | Bit 2 | Bit 1 | Bit 0 |

| da7                      | da6    | da5     | da4        | da3      | da2   | da1   | da0   |

| Base Addre               | ss + D |         |            |          |       |       |       |

| Bit 7                    | Bit 6  | Bit 5   | Bit 4      | Bit 3    | Bit 2 | Bit 1 | Bit 0 |

| Х                        | Х      | Х       | Х          | da11     | da10  | da9   | da8   |

da11-da0 -> DAC 0 data

Writing a 12-bit value to this address will output the corresponding voltage on DAC 0 (refer the Option Selection map for output voltage range). If the DAC simultaneous bit (Base Address + 10, bit 1) is set, then DAC 0's output will update after writing to DAC 1.

## Base Address + E-F (write) DAC 1 Output Data

Base Address + E

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| da7   | da6   | da5   | da4   | Da3   | da2   | da1   | da0   |

#### Base Address + F

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Χ     | Х     | Х     | Х     | da11  | da10  | da9   | da8   |

da11-da0 -> DAC 1 data

Writing a 12-bit value to this address will output the corresponding voltage on DAC 1 (refer the Option Selection map for output voltage range).

Base Address + 10 (write) DAC Configuration

| - |       |       | (     |       | - 3   |       |       |              |

|---|-------|-------|-------|-------|-------|-------|-------|--------------|

|   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0        |

|   | Χ     | Χ     | Χ     | Х     | Х     | Х     | Χ     | simultaneous |

simultaneous -> '0' = DACs update when written '1' = DACs update upon write to DAC 1

Writing a '1' to Bit 0 will set the DAC simultaneous bit. This causes both DACs to be updated on a write to DAC 1.

Base Address + 11 (write) A/D Start & Counter/Timer 0 Clock Configuration

|       |       | 1     |        |           |           |              |              |

|-------|-------|-------|--------|-----------|-----------|--------------|--------------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2     | Bit 1        | Bit 0        |

| Х     | Х     | Х     | clkSrc | startEdge | startType | startSource1 | startSource0 |

Writing to this address will configure the A/D Start Source, A/D Start Type, A/D Start as rising or falling edge, and Counter/Timer 0's clock source. Below are the different configuration bit patterns:

#### A/D Start Source

Software → startSource0 = '0'; startSource1 = '0'

Timer → startSource0 = '1'; startSource1 = '0'

External → startSource0 = '0'; startSource1 = '1'

#### A/D Start Type

Single Channel → startType = '0'

Scan → startType = '1'

## A/D Start Edge

Rising → startEdge = '0'

Falling → startEdge = '1'

#### Counter/Timer0 Clock

Internal 10MHz → clkSrc = '0'

External Pin → clkSrc = '1'

Base Address + 12 (read) A/D, DAC, FIFO Status Flags

| Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1        | Bit 0   |

|----------|----------|-------|-------|-------|----------|--------------|---------|

| fifoFull | halfFull | empty | dac1  | dac0  | gainMode | single-ended | bipolar |

Reading from this address will show the status of the following flags:

| bipolar      | $\rightarrow$ | '0' = jumpers set to unipolar '1' = jumpers set to bipolar                    |

|--------------|---------------|-------------------------------------------------------------------------------|

| single-ended | $\rightarrow$ | '0' = jumpers set to differential '1' = jumpers set to single-ended           |

| gainMode     | $\rightarrow$ | '0' = jumpers set to GNL '1' = jumpers set to GNH                             |

| dac0         | $\rightarrow$ | '0' = DAC 0 has 0-10V range '1' = DAC 0 has 0-5V range                        |

| dac1         | $\rightarrow$ | '0' = DAC 1 has 0-10V range '1' = DAC 1 has 0-5V range                        |

| empty        | $\rightarrow$ | '0' = A/D Data FIFO is empty '1' = A/D Data FIFO is not empty                 |

| halfFull     | $\rightarrow$ | '0' = A/D FIFO is at least half full '1' = A/D FIFO is not at least half full |

| fifoFull     | $\rightarrow$ | '0' = A/D Data FIFO is full '1' = A/D Data FIFO is not full                   |

## Base Address + 13 (read/write) IRQ Configuration and Status

Base Address + 13 write

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2         | Bit 1    | Bit 0    |

|-------|-------|-------|-------|-----------|---------------|----------|----------|

| Х     | X     | X     | X     | fullIrqEn | halfFullIrqEn | eosIrqEn | eocIrqEn |

Writing to this address will configure the IRQs for End of Conversion (EOC), End of Scan (EOS), A/D Data FIFO at least half full, and A/D Data FIFO full. Below are the IRQ enable bit patterns:

| eocIrqEn      | $\rightarrow$ | '0' = disable the EOC IRQ       | '1' = enable the EOC IRQ       |

|---------------|---------------|---------------------------------|--------------------------------|

| eosIrqEn      | $\rightarrow$ | '0' = disable the EOS IRQ       | '1' = enable the EOS IRQ       |

| halfFullIrqEn | $\rightarrow$ | '0' = disable the A/D Data FIFO | '1' = enable the A/D Data FIFO |

|               |               | is at least half full IRQ       | is at least half full IRQ      |

| fullIrqEn     | $\rightarrow$ | '0' = disable the A/D Data FIFO | '1' = enable the A/D Data FIFO |

|               |               | full IRQ                        | full IRQ                       |

#### Base Address + 13 read

| Dasc / laarc | ,55 · 10 10aa |        |        |       |       |       |       |

|--------------|---------------|--------|--------|-------|-------|-------|-------|

| Bit 7        | Bit 6         | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| fullirg      | halfFullIrg   | eosIrq | eoclrq | Х     | Χ     | Х     | Χ     |

Once any of the above IRQ enables are set to '1', the corresponding condition will cause an IRQ to be generated. All four enables can be set at the same time. A read of this address allows the ability to see which IRQ flag generated the IRQ. Below are the IRQ flags:

| eoclrq      | $\rightarrow$ | '0' = no EOC IRQ occurred       | '1' = EOC IRQ occurred       |

|-------------|---------------|---------------------------------|------------------------------|

| eosIrq      | $\rightarrow$ | '0' = no EOS IRQ occurred       | '1' = EOS IRQ occurred       |

| halfFullIrq | $\rightarrow$ | '0' = no A/D FIFO is at least   | '1' = A/D FIFO is at least   |

| •           |               | half full IRQ occurred          | half full IRQ occurred       |

| fullIrq     | $\rightarrow$ | '0' = no FIFO full IRQ occurred | '1' = FIFO full IRQ occurred |

Reading this address also clears any of the IRQ flags that are set.

#### Base Address + 14 (read/write) Port A DIO (8255)

|       |       |       |       | ( /   |       |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| a7    | a6    | a5    | a4    | a3    | a2    | a1    | a0    |

#### a7-a0 -> Port A data

Reading from this address will return the digital data on Port A. Writing to this address will output the digital data on Port A. Readback is supported while in the output mode. Be sure to refer to Base Address + 17 for controlling Port A's input/output direction.

| Base Address + 15 | (read/write) | Port B DIO | (8255) |

|-------------------|--------------|------------|--------|

|-------------------|--------------|------------|--------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| b7    | b6    | b5    | b4    | b3    | b2    | b1    | b0    |

#### b7-b0 -> Port B data

Reading from this address will return the digital data on Port B. Writing to this address will output the digital data on Port B. Readback is supported while in the output mode. Be sure to refer to Base Address + 17 for controlling Port B's input/output direction.

#### Base Address + 16 Unused

Base Address + 17 (write) DIO Configuration (8255)

| Bit 7       | Bit 6 | Bit 5 | Bit 4    | Bit 3 | Bit 2 | Bit 1    | Bit 0 |

|-------------|-------|-------|----------|-------|-------|----------|-------|

| modeSetFlag | Х     | X     | PortADir | Х     | Х     | portBDir | Х     |

Writing to this address configures the input/output direction for Ports A and B. A '1' must always be written to bit 7 when configuring. Below are the Port direction bits:

modeSetFlag → '0' = configuration not enabled '1' = configuration enabled portADir → '0' = Port A is output '1' = Port A is input (default) o'' = Port B is output '1' = Port B is input (default)

## Base Address + 18 (read/write) EEPROM access

Base Address + 18 read

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| data  | X     | X     | X     | X     | X     | X     | X     |

#### Base Address + 18 write

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| data  | Х     | Х     | Х     | Х     | Х     | Х     | SCIk  |

The EEPROM is intended to hold calibration data for the A/D Gain and Offset correction, and the Gain Correction data for both DACs. Calibration is only needed for GNL/GNH and BIP/UNI jumper selected ranges, so a total of 4 A/D Input calibration data pairs are used. Consult the provided calibration program or sample code for information on the locations in the EEPROM used to store the calibration data.

Although the EEPROM is intended to contain calibration data, it is unlikely your program will need to keep calibration data for the ranges you are not going to use. In this case you can use those locations in the EEPROM for your own purposes.

#### Writing to the EEPROM

In order to write to the EEPROM, an enable code and start bit must be transmitted, then the write opcode (2 bits, 01) followed by the address location of the data to be loaded into the EEPROM (6 bits, MSB first), followed by the data (16bits, MSB first). Then the transmission is ended with 00. Therefore, to write a value of aa55 to location 5, you would perform the following 27 writes:

| Write | Value                         | Description                                                                                               |

|-------|-------------------------------|-----------------------------------------------------------------------------------------------------------|

| 1     | 1xxxxxx0 = 80                 | Enable code. Always write 80 as the 1 <sup>st</sup> byte                                                  |

| 2     | 1xxxxxx1 = 81                 | Start Bit. Always write 81 as the 2 <sup>nd</sup> byte                                                    |

| 3     | 0xxxxxx1 = 01                 | opcode bit 1, always write 01 as the 3 <sup>rd</sup> byte for EEPROM writing                              |

| 4     | 1xxxxxx1 = 81                 | opcode bit 0, always write 81 as the 4 <sup>th</sup> byte for EEPROM writing                              |

| 5     | 0xxxxxx1 = 01                 | MSB of address. Bit 7 should be 1 or 0 based on the D5 bit of address to be written. Always set D0 to "1" |

| 6     | <b>0</b> xxxxxx1 = <b>0</b> 1 | Bit 7 should be bit D4 of address. Always set D0 to "1"                                                   |

| 7     | <b>0</b> xxxxxx1 = <b>0</b> 1 | Bit 7 should be bit D3 of address. Always set D0 to "1"                                                   |

| 8     | 1xxxxxx1 = 81                 | Bit 7 should be bit D2 of address. Always set D0 to "1"                                                   |

| 9     | <b>0</b> xxxxxx1 = <b>0</b> 1 | Bit 7 should be bit D1 of address. Always set D0 to "1"                                                   |

| 10    | 1xxxxxx1 = <b>8</b> 1         | LSB of address. Bit 7 should be 1 or 0 based on the D0 bit of address to be written. Always set D0 to "1" |

| 11    | 1xxxxxx1 = 81                 | MSB of data. Bit 7 should be 1 or 0 based on the D15 bit of address to be written. Always set D0 to "1"   |

| 12    | <b>0</b> xxxxxx1 = <b>0</b> 1 | Bit 7 should be bit D14 of data. Always set D0 to "1"                                                     |

| 13    | 1xxxxxx1 = 81                 | Bit 7 should be bit D13 of data. Always set D0 to "1"                                                     |

| 14    | <b>0</b> xxxxxx1 = <b>0</b> 1 | Bit 7 should be bit D12 of data. Always set D0 to "1"                                                     |

| 15    | 1xxxxxx1 = <b>8</b> 1         | Bit 7 should be bit D11 of data. Always set D0 to "1"                                                     |

| 16    | <b>0</b> xxxxxx1 = <b>0</b> 1 | Bit 7 should be bit D10 of data. Always set D0 to "1"                                                     |

| 17    | 1xxxxxx1 = <b>8</b> 1         | Bit 7 should be bit D9 of data. Always set D0 to "1"                                                      |

| 18    | <b>0</b> xxxxxx1 = <b>0</b> 1 | Bit 7 should be bit D8 of data. Always set D0 to "1"                                                      |

| 19    | <b>0</b> xxxxxx1 = <b>0</b> 1 | Bit 7 should be bit D7 of data. Always set D0 to "1"                                                      |

| 20    | 1xxxxxx1 = 81                 | Bit 7 should be bit D6 of data. Always set D0 to "1"                                                      |

| 21    | <b>0</b> xxxxxx1 = <b>0</b> 1 | Bit 7 should be bit D5 of data. Always set D0 to "1"                                                      |

| 22    | 1xxxxxx1 = <b>8</b> 1         | Bit 7 should be bit D4 of data. Always set D0 to "1"                                                      |

| 23    | <b>0</b> xxxxxx1 = <b>0</b> 1 | Bit 7 should be bit D3 of data. Always set D0 to "1"                                                      |

| 24    | 1xxxxxx1 = <b>8</b> 1         | Bit 7 should be bit D2 of data. Always set D0 to "1"                                                      |

| 25    | <b>0</b> xxxxxx1 = <b>0</b> 1 | Bit 7 should be bit D1 of data. Always set D0 to "1"                                                      |

| 26    | 1xxxxxx1 = <b>8</b> 1         | LSB of data. Bit 7 should be 1 or 0 based on the D0 bit of data written. Always set D0 to "1"             |

| 27    | <b>0</b> xxxxxx0= <b>0</b> 0  | End. Always write 00 as the 27 <sup>th</sup> byte                                                         |

For ease of reference the bits which can change are typeset in  $\boldsymbol{bold}.$

There must be a least a  $4\mu s$  delay between each of the 27 write operations to the EEPROM. After the last write operation which ends communication with the EEPROM, it will be unavailable for 20mS. Do not access the EEPROM during this period.

Please note, it is not possible to write to the EEPROM until an EEPROM WRITE ENABLE (EWREN) sequence has been written to Base + A. The EWREN sequence consists of the following bytes, in order: 81, 01, 01, 81, 81, 01, 01, 01, 01, 00.

Once the EWREN sequence has been written it is possible to write to the EEPROM as desired. If you wish to subsequently disable writes to the EEPROM, a disable sequence of bytes may be written to Base + A as follows: 81, 01, 01, 01, 01, 01, 01, 01, 00.

## Reading from the EEPROM

Similarly, reading a word takes 10 writes (enable code, start bit, read opcode (2 bits 1,0) and the address (6 bits, MSB first)), followed by 16 reads to acquire the data from the EEPROM, followed by one write to terminate communication with the EEPROM. Therefore, to read from address 4, perform the following writes and reads:

| Write    | Value                                                                 | Description                                                                                                          |

|----------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 1        | 1xxxxxx0 = 80                                                         | Enable code. Always write 80 as the 1 <sup>st</sup> byte                                                             |

| 2        | 1xxxxxx1 = 81                                                         | Start Bit. Always write 81 as the 2 <sup>nd</sup> byte.                                                              |

| 3        | 1xxxxxx1 = 81                                                         | Opcode Bit 1. Always write 81 as the 3 <sup>rd</sup> byte for reading                                                |

| 4        | 0xxxxxx1 = 01                                                         | Opcode Bit 0. Always write 01 as the 4 <sup>th</sup> byte for reading                                                |

| 5        | <b>0</b> xxxxxx1 = <b>0</b> 1                                         | MSB of address. Bit 7 should be 1 or 0 based on the D5 bit of address in the EEPROM to be Read. Always set D0 to "1" |

| 6        | $0\mathbf{x}\mathbf{x}\mathbf{x}\mathbf{x}\mathbf{x}\mathbf{x}1 = 01$ | Bit 7 should be bit D4 of address. Always set D0 to "1"                                                              |

| 7        | $0\mathbf{x}\mathbf{x}\mathbf{x}\mathbf{x}\mathbf{x}\mathbf{x}1 = 01$ | Bit 7 should be bit D3 of address. Always set D0 to "1"                                                              |

| 8        | 1xxxxxx1 = <b>8</b> 1                                                 | Bit 7 should be bit D2 of address. Always set D0 to "1"                                                              |

| 9        | $0\mathbf{x}\mathbf{x}\mathbf{x}\mathbf{x}\mathbf{x}\mathbf{x}1 = 01$ | Bit 7 should be bit D1 of address. Always set D0 to "1"                                                              |

| 10       | <b>0</b> xxxxxx1 = <b>0</b> 1                                         | LSB of address. Bit 7 should be 1 or 0 based on the D0 bit of address to be read. Always set D0 to "1"               |

| Read 1   |                                                                       | Bit D7 of this Read returns the Most Significant Bit (D15) of the 16-bit data                                        |

|          |                                                                       | stored at the address specified in writes 4 through 9.                                                               |

| Read 2   |                                                                       | D7 contains bit D14 from the word at the specified address                                                           |

| Read 3   |                                                                       | D7 contains bit D13 from the word at the specified address                                                           |

| Read 4   |                                                                       | D7 contains bit D12 from the word at the specified address                                                           |

| Read 5   |                                                                       | D7 contains bit D11 from the word at the specified address                                                           |

| Read 6   |                                                                       | D7 contains bit D10 from the word at the specified address                                                           |

| Read 7   |                                                                       | D7 contains bit D9 from the word at the specified address                                                            |

| Read 8   |                                                                       | D7 contains bit D8 from the word at the specified address                                                            |

| Read 9   |                                                                       | D7 contains bit D7 from the word at the specified address                                                            |

| Read 10  |                                                                       | D7 contains bit D6 from the word at the specified address                                                            |

| Read 11  |                                                                       | D7 contains bit D5 from the word at the specified address                                                            |

| Read 12  |                                                                       | D7 contains bit D4 from the word at the specified address                                                            |

| Read 13  |                                                                       | D7 contains bit D3 from the word at the specified address                                                            |

| Read 14  |                                                                       | D7 contains bit D2 from the word at the specified address                                                            |

| Read 15  |                                                                       | D7 contains bit D1 from the word at the specified address                                                            |

| Read 16  |                                                                       | D7 contains bit D0 from the word at the specified address                                                            |

| Write 11 | 0xxxxxx0 = 00                                                         | End. Always write 00 as the last step                                                                                |

For ease of reference the bits which can change are typeset in **bold**.

There must be a least a  $4\mu$ s delay between each of the 11 write and 16 read operations to the EEPROM. After the last write operation which ends communication with the EEPROM, it will be unavailable for 20mS. Do not access the EEPROM during this period.

The Software Master CD contains sample programs demonstrating the use of the EEPROM in a variety of languages, including a "driverlet" which encapsulates the complexities of the process. Using this "driverlet" is as simple as passing the address and data in the EEPROM you wish to write, or the address from which to read, to our functions. It is highly recommended that you use the provided source code as a basis for your own programs.

Base Address + 19 (write) Calibration access

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| data  | X     | X     | X     | X     | X     | X     | SClk  |

The board contains 4 digital potentiometers used to calibrate the device. The four calibration corrections provided are: A/D Offset (00), A/D Gain (01), Gain for DAC0 (10), and DAC1 (11). These four corrections are internally addressed 0, 1, 2, and 3. Each calibration correction consists of a value from 0 - 255 (8 bits) corresponding to the internal value of the digital potentiometer.

A/D Offset corresponds to the "B" in a Y=mX+B equation. A/D Gain is the "m" term of the same equation. DAC Gain represents "m" in the equation Y=mX. The nature of the DAC circuitry eliminates the need to provide offset (B) calibration.

The value you load into these calibration potentiometers is normally read from the EEPROM and written here only during program initialization, and only needs to be written once per power-on cycle.

To load one of the calibration correction values you must write the address (0-3) of the correction you wish to load, the 8-bit value you wish to load, and an End byte.

Similar to the operation of the EEPROM, the calibration correction values are loaded serially into the digital potentiometers in the board. Therefore, to load a value of 4F into the A/D Gain potentiometer, the following writes are performed:

| Write | Value       | Description                                                                     |

|-------|-------------|---------------------------------------------------------------------------------|

| 1     | 1xxxxxx0=80 | Enable code. Always write 80 as the 1 <sup>st</sup> byte                        |

| 2     | 0xxxxxx1=01 | These two bits are the address of the potentiometer to write. 00 is A/D offset, |

| 3     | 1xxxxxx1=81 | 01 is gain, 10 is DAC0 gain, 11 is DAC1 gain. Write 2 is MSB, Write 3 is LSB.   |

| 4     | 0xxxxxx1=01 | MSB of data. Bit D7 of Write 4 should be the D7 bit of the calibration          |

|       |             | correction value you are loading.                                               |

| 5     | 1xxxxxx1=81 | D7 should be bit D6 of the calibration value                                    |

| 6     | 0xxxxxx1=01 | D7 should be bit D5 of the calibration value                                    |

| 7     | 0xxxxxx1=01 | D7 should be bit D4 of the calibration value                                    |

| 8     | 1xxxxxx1=81 | D7 should be bit D3 of the calibration value                                    |

| 9     | 1xxxxxx1=81 | D7 should be bit D2 of the calibration value                                    |

| 10    | 1xxxxxx1=81 | D7 should be bit D1 of the calibration value                                    |

| 11    | 1xxxxxx1=81 | D7 should be bit D0 of the calibration value                                    |

| 12    | 0xxxxxx1=01 | End. Always Write 00 as the last step                                           |

For ease of reference the bits which can change are typeset in **bold**.

For details on the operation of the Digital Potentiometer, refer to the Analog Devices AD8403 datasheet.

#### Base Address + 1A Unused

Base Address + 1B (write) Reset Register

| Baco / taal t | , בו י טטט | 11110) | riocot riogi | Root Rogistor |          |             |           |  |

|---------------|------------|--------|--------------|---------------|----------|-------------|-----------|--|

| Bit 7         | Bit 6      | Bit 5  | Bit 4        | Bit 3         | Bit 2    | Bit 1       | Bit 0     |  |

| Х             | Х          | Х      | masterReset  | dacReset      | dioReset | digPotReset | fifoReset |  |

Writing to this address will reset the following:

| fifoReset   | $\rightarrow$ | '0' = N/A | '1' = reset the A/D Data FIFO                              |

|-------------|---------------|-----------|------------------------------------------------------------|

| digPotReset | $\rightarrow$ | '0' = N/A | '1' = reset the digital calibration potentiometers         |

| dioReset    | $\rightarrow$ | '0' = N/A | '1' = reset the 8255 Port A and Port B                     |

| dacReset    | $\rightarrow$ | '0' = N/A | '1' = reset the DACs back to zero                          |

| masterReset | $\rightarrow$ | '0' = N/A | '1' = reset all of the above + all configuration addresses |

23

Base Address + 1C - 1E Unused

| Base Addre | ess + 1F ( | (read) | Board Mode | el    |       |       |       |

|------------|------------|--------|------------|-------|-------|-------|-------|

| Bit 7      | Bit 6      | Bit 5  | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| 0          | 0          | 0      | 0          | 0     | 0     | 104E  | 104A  |

Reading from this address will indicate the presence and model number, or absence of the board.

104A  $\rightarrow$  '0' = N/A '1' = "104A" model detected Byte value = "01" 104E  $\rightarrow$  '0' = N/A '1' = "104E" model detected Byte value = "02"

No card detected Byte value = "FF"

## **Chapter 6: Connector Pin Assignments**

| Pin | Signal Name        | Description                                                              | Pin | Signal Name         | Description                                                          |

|-----|--------------------|--------------------------------------------------------------------------|-----|---------------------|----------------------------------------------------------------------|

| 1   | Ch0(SE)/Ch0+(DIFF) | Channel 0 Singled-ended or<br>Channel 0 differential non-inverting input | 2   | Ch8(SE)/Ch0-(DIFF)  | Channel 8 Single-ended or<br>Channel 0 differential inverting input  |

| 3   | AGND               | Analog Ground                                                            | 4   | Ch9(SE)/Ch1-(DIFF)  | Channel 9 Single-ended or<br>Channel 1 differential inverting input  |

| 5   | Ch1(SE)/Ch1+(DIFF) | Channel 1 Singled-ended or<br>Channel 1 differential non-inverting input | 6   | AGND                | Analog Ground                                                        |

| 7   | Ch2(SE)/Ch2+(DIFF) | Channel 2 Singled-ended or<br>Channel 2 differential non-inverting input | 8   | Ch10(SE)/Ch2-(DIFF) | Channel 10 Single-ended or<br>Channel 2 differential inverting input |

| 9   | AGND               | Analog Ground                                                            | 10  | Ch11(SE)/Ch3-(DIFF) | Channel 11 Single-ended or<br>Channel 3 differential inverting input |

| 11  | Ch3(SE)/Ch3+(DIFF) | Channel 3 Singled-ended or<br>Channel 3 differential non-inverting input | 12  | AGND                | Analog Ground                                                        |

| 13  | Ch4(SE)/Ch4+(DIFF) | Channel 4 Singled-ended or<br>Channel 4 differential non-inverting input | 14  | Ch12(SE)/Ch4-(DIFF) | Channel 12 Single-ended or<br>Channel 4 differential inverting input |

| 15  | AGND               | Analog Ground                                                            | 16  | Ch13(SE)/Ch5-(DIFF) | Channel 13 Single-ended or<br>Channel 5 differential inverting input |

| 17  | Ch5(SE)/Ch5+(DIFF) | Channel 5 Singled-ended or<br>Channel 5 differential non-inverting input | 18  | AGND                | Analog Ground                                                        |

| 19  | Ch6(SE)/Ch6+(DIFF) | Channel 6 Singled-ended or<br>Channel 6 differential non-inverting input | 20  | Ch14(SE)/Ch6-(DIFF) | Channel 14 Single-ended or<br>Channel 6 differential inverting input |

| 21  | AGND               | Analog Ground                                                            | 22  | Ch15(SE)/Ch7-(DIFF) | Channel 15 Single-ended or<br>Channel 7 differential inverting input |

| 23  | Ch7(SE)/Ch7+(DIFF) | Channel 7 Singled-ended or<br>Channel 7 differential non-inverting input | 24  | AGND                | Analog Ground                                                        |

| 25  | DAC 0              | Digital to Analog Output Channel 0                                       | 26  | DAC 1               | Digital to Analog Output Channel 1                                   |

Table 6-1: P1, 26-pin Right-Angle Header, Analog Inputs, Analog Outputs

# Pin Type Key

- ▼ Ground

- Counter

- x Not Connected

- Power

- Analog Input

- Analog Output

- Digital I/O

| Pin | Signal Name            | Description                                                                                                             | Pin | Signal Name | Description    |

|-----|------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|-------------|----------------|

| 1   | DIO 0                  | Digital I/O Bit 0 (pulled-up)                                                                                           |     | DGND        | Digital Ground |

| 3   | DIO 1                  | Digital I/O Bit 1 (pulled-up)                                                                                           |     | DGND        | Digital Ground |

| 5   | DIO 2                  | Digital I/O Bit 2 (pulled-up)                                                                                           | 6   | DGND        | Digital Ground |

| 7   | DIO 3                  | Digital I/O Bit 3 (pulled-up)                                                                                           | 8   | DGND        | Digital Ground |

| 9   | DIO 4                  | Digital I/O Bit 4 (pulled-up)                                                                                           | 10  | DGND        | Digital Ground |

| 11  | DIO 5                  | Digital I/O Bit 5 (pulled-up)                                                                                           | 12  | DGND        | Digital Ground |

| 13  | DIO 6                  | Digital I/O Bit 6 (pulled-up)                                                                                           | 14  | DGND        | Digital Ground |

| 15  | DIO 7                  | Digital I/O Bit 7 (pulled-up)                                                                                           | 16  | DGND        | Digital Ground |

| 17  | DIO 8                  | Digital I/O Bit 8 (pulled-up)                                                                                           | 18  | DGND        | Digital Ground |

| 19  | DIO 9                  | Digital I/O Bit 9 (pulled-up)                                                                                           | 20  | DGND        | Digital Ground |

| 21  | DIO 10                 | Digital I/O Bit 10 (pulled-up)                                                                                          | 22  | DGND        | Digital Ground |

| 23  | DIO 11                 | Digital I/O Bit 11 (pulled-up)                                                                                          | 24  | DGND        | Digital Ground |

| 25  | DIO 12                 | Digital I/O Bit 12 (pulled-up)                                                                                          | 26  | DGND        | Digital Ground |

| 27  | DIO 13                 | Digital I/O Bit 13 (pulled-up)                                                                                          | 28  | DGND        | Digital Ground |

| 29  | DIO 14                 | Digital I/O Bit 14 (pulled-up)                                                                                          | 30  | DGND        | Digital Ground |

| 31  | DIO 15                 | Digital I/O Bit 15 (pulled-up)                                                                                          | 32  | DGND        | Digital Ground |

| 33  | Unused                 | No connection                                                                                                           | 34  | DGND        | Digital Ground |

| 35  | KEY                    |                                                                                                                         | 36  |             | KEY            |

| 37  | Counter/Timer 0 Clock  | Clock 8254 Counter/Timer 0 Clock (input; pulled up)                                                                     |     | DGND        | Digital Ground |

| 39  | External Start Trigger | External Analog to Digital Conversion Start<br>Trigger (input; pulled-up; software selectable<br>rising / falling edge) | 40  | DGND        | Digital Ground |

| 41  | Counter/Timer 0 Out    | Output from 8254 Counter/Timer 0 (output)                                                                               | 42  | DGND        | Digital Ground |

| 43  | Counter/Timer 2 Out    | Output from 8254 Counter/Timer 2 (output)                                                                               | 44  | DGND        | Digital Ground |

Table 6-2: P2, 44-pin Right-Angle Header, Digital I/O & Counter/Timers

IDC 8-Pin Header Male

2 1 1 1 8

1 7

| Pin | Signal | Pin | Signal |

|-----|--------|-----|--------|

| 1   | Ground | 2   | Ground |

| 3   | Ground | 4   | +12V   |

| 5   | Ground | 6   | -12V   |

| 7   | Ground | 8   | Ground |

Table 6-3: P3, 8-pin Right-Angle Header, External Power

See Chapter 3: Option Selection for jumper configuration information for power options.

## **Chapter 7: Specifications**

**Analog Inputs**

ADC Type Successive approximation

Sampling rate "16A" version: 500ksamples/sec (maximum aggregate)

"16E" version: 250ksamples/sec (maximum aggregate)

Resolution 16-bit

Number of channels 16 single-ended or 8 differential (jumper selectable)

Bipolar ranges ±0.5V, ±1, ±2V, ±2.5V, ±5V, and ±10V (jumper+software selectable)

Unipolar ranges 0-1V, 0-2V, 0-5V, 0-10V (jumper+software selectable)

Board Calibration Programmable Digital Potentiometers to calibrate for gain/offset error

System Calibration Program provided to calibrate entire system

Input impedance  $1M\Omega$

A/D Start Sources Software Start, Timer Start, and External Start Trigger

(rising or falling edge; software selectable) Single Channel or Scan (software selectable)

Channel Oversampling 0-255 consecutive samples/channel (software selectable)

Overvoltage protection -40 to +55V Crosstalk 60dB @ 400kHz

**Analog Outputs**

A/D Start Types

Channels 2 Resolution 12-bit

Voltage Ranges 0-5V, 0-10V (jumper selectable)

Conversion Frequency 100k conversions/sec

Simultaneous Update Yes

Digital I/O

Type 8255 (Port A and Port B only)

Lines 16, programmable as inputs or outputs in groups of 8 (pulled-up)

Input voltage Logic low: 0V(min) to 0.8V(max)

Logic high: 2V(min) to 5V(max)

Logic low: 0V(min) to 0.55V(max)

Logic high: 2V(min) to 5V(max)

Output current Logic low 24mA(max) sink

Logic high 24mA(max) source

Counter/Timer

Output voltage

Type 82C54 programmable interval counter

Available Counters Counter 0

Input Frequency 10MHz (max)

Counter size 16-bit

Clock Internal 10MHz or Externally supplied (software selectable; pulled-up)

Clock Period 100ns (min)

Clock Pulse Width High/Low 30ns (min)/40ns (min) Input/Output Voltage/Current Same as Digital I/O

**Environmental**

Operating Temperature 0° to +70°C, optional -40° to +85°C

Storage Temperature -40° to +105°C

Humidity 5% to 90% RH, without condensation

Power required Bus powered: +5V at 40mA typical w/ no external I/O connections

+12V at 24mA ""

-12V at 23mA ""

DC/DC option: +5V at 180mA typical w/ no ext. I/O connections

## **Appendix A: 82C54 Counter Timer Operation**

The board contains one type 8254 programmable counter/timer. The 8254 consists of three, 16-bit, presettable down-counters. Each counter can be programmed to any count between 2 and 65,535 in binary format, depending on the mode chosen. The programmed value is a divisor and the output frequency equals the input frequency divided by the programmed value.

In this manual these three counter/timers are designated Counter/Timer 0, Counter/Timer 1, and Counter/Timer 2. Counter/Timer 0 is for general use. Counter/Timer 1's output in the clock input to Counter/Timer 2. The output of Counter/Timer 2 is used for A/D Start or for general use (timer not needed for A/D Start). Refer to the block diagram for more information.

## **Operational Modes**